tpd、tcd - 最高时钟频率、pipeline、模块延迟时间优化

大后天就要回大泉州啦,这次具体说说之前搞不懂的tcd、tpd以及由什么决定设计的最高时钟频率,同时比较有趣的还有从洗衣房问题出发的pipeline设计思路、最后思考了如何将模块8ns的延迟时间变为4ns,还没看下面具体的讲解可以先想想已知一个模块的延时时间是8ns如何将其降低

tpd、tcd的定义

- tpd - 传输延迟时间 - 输入信号有效后,到输出信号有效之间的时间差

- tcd - 无效延迟时间 - 就是输入信号开始变化,到输出信号开始变化的时间差

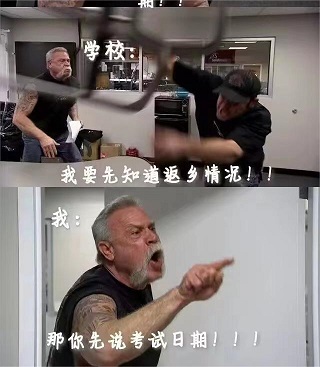

如图列举了一个简单的逻辑电路设计图,对于reg2当上升沿到来时来说需要保证持续时间的长度小于前面模块的无效延迟时间,这样才能保证上一个数据的有效性

- 而针对此电路的最高时钟频率:应该看t2,上升沿到来时,需要经过两个

tpd(reg1、1),reg2D端才能拿到有效值,此时需要再经过tsetupD触发器才能完成数据输入。 - 故可以推出图中的两个约束不等式,也可以看出影响整体工作的时钟频率的主要因素是tpd即传输延迟时间

通过上述的一个设计实例就可以引出如何提高设计的传输延迟时间的思考,当然可以通过优化器件内部结构来实现,但如果想从外围电路入手应该怎么实现呢

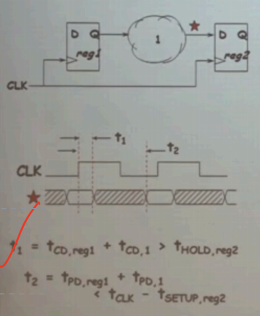

- 下面我们提出问题如何将一个逻辑电路模块成品(tpd = 8ns)优化为4ns器件

- 提升不了整体的工作频率是因为这时候传输延迟时间需要与时钟频率配合确保每一次输入数据的有效性,可以这样想如果我有两个然后让其并联,让两个器件工作分别工作在储存和传输的状态,是不是就可以实现效率的倍增,而我应该有一个器件来控制的两个数据输出的时间,那就很明显 - 当然是触发器

这边采用的是简易的D触发器,因为只要实现简单的数据输入操作,也可以采用J/K触发器,如果是接D触发器这边通过从输出端Q接反相器到输入端来实现0、1切换的有限状态机

而上面的两个用的是电平触发的D触发器

工作状态:当C0接收数据的时候;C1传递数据给后方的数据选择器,相当于把8ns变为两个4ns,用时序图来理解 - 实现两个模块有个4ns的相差

通过外围电路设计就实现了模块传输演出时间的优化,而在实际电路中如果要提高整体的工作频率,也是通过降低电路中的tpd max,这种设计思路也有个称呼 - pipeline(组合电路+寄存器)

pipeline

- 前面的思考还是不少,这边就来有趣的引例调调味吧

eg. 现在sbu的德馨室有一个洗衣机、一个干衣机(虽然目前没有 - 毕竟是假设嘛)假设洗衣机的工作时间为30min、而干衣机的工作时间为60min,我们可以对比下面两种方案

- A宿舍同学只有当干衣机不工作时,才将下一桶衣服放入洗衣机

- B宿舍同学只要空着就用

- 分析下就可以得到A宿舍运行起来后的每桶运用的有效时间为90min、而B宿舍运行起来后每桶的有效时间为60min - 这是因为在B宿舍在干衣机工作时,下一桶衣服已经进入洗衣机内开始了工作,相当于有个地方来放置已经洗好的衣服然后等上一桶洗完这边就继续放入

虽然上面这个例子挺sbu的,但是还是挺能反映pipeline的设计思路

- pipeline = 组合电路 + 寄存器

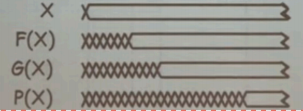

在F、G,模块传输完成后可以先将其存入寄存器(暂存器)中然后先就进行下一轮的数据输入也不影响将这一轮的数据置入P模块

最近可以说是又一个疫情寒冬了,下面这个哈哈