发散性思维-点点思考-CMOS、TTL的开关特性差异、关于传输延迟时间的理解、温度与二极管击穿

主要就是最近数电实验做的CMOS和TTL的传输特性曲线引发了我的思考,为什么CMOS的开关特性明明比TTL好,但是最终的传输延迟时间反而比TTL慢?还有就是关于传输延迟时间的一些自我理解,感觉课本上讲述的也比较模糊,最后就是搜资料的时候发现的温度影响二极管击穿是有两种方式

CMOS、TTL的特性差异

输入电压范围:CMOS的范围较大(5~15V)、TTL在5V以下

功耗:CMOS的功耗较小、TTL较大

噪声容限:CMOS的噪声容限比TTL大

影响速度的因素:TTL主要受电路内部管子的开关特性、电路结构、各电阻的阻值影响、CMOS主要在于外部,负载电容C是影响其工作速度的原因

抗干扰能力:CMOS内部是MOSFET,输入总抗很大,对干扰信号的捕捉能力很强,所以不用的管脚不要悬空,需要接上拉或下拉电阻,同时给予一个电平

上面这边简单阐述了几个关于CMOS、TTL的特性差异,但是为什么CMOS的传输特性如此之好,而传输延迟时间却比TTL拉呢。

这边其实不然,这我只是建立在CMOS和TTL没有经过改进的前提下,因为比如TI的74HC系列CMOS反相器已经可以做到9ns了,而且后面还有很多进一步ADVANCED

要想知道这个原因就得先搞清楚传输延迟时间是如何计算的

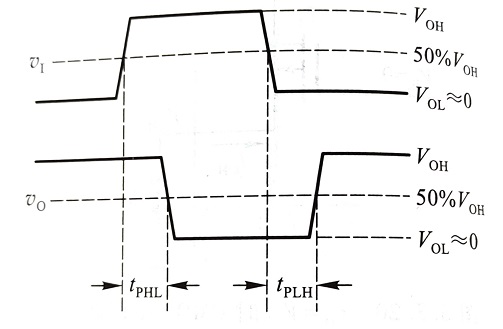

传输延迟时间

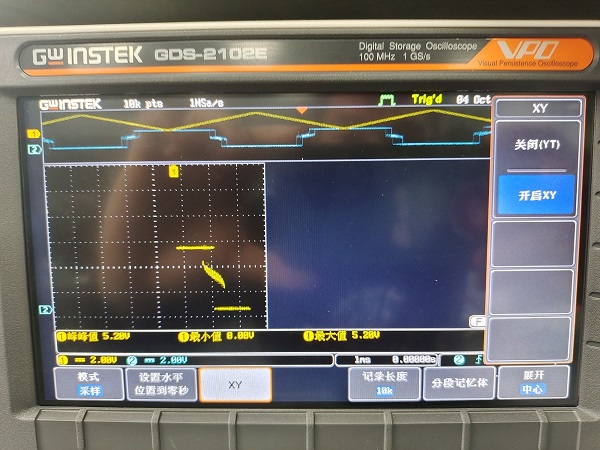

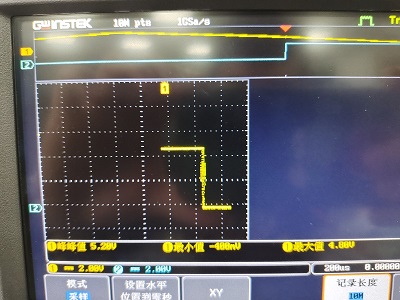

延迟顾名思义就是输出电压落后于输入电压的时间,且记低电平跳变为高电平的传输延迟时间为tPLH、高电平跳变为低电平的传输延迟时间记为tPHL,在CMOS电路中两者通常是相等的,但在TTL中由于三极管的导通状态不一致,两者是不相同的。

- 具体定义:输入和输出波形对应边上等于最大幅度50%的两点的时间间隔。

为了更好的量化传输延迟时间,以此来探究影响传输延迟时间的主要因子,就得讲讲RC全响应

全响应

在电路中由电源激励和储能元件初始状态下非零条件下产生的响应

$$

U_t=U_\infty+(U_0-U_\infty)·e^{-\frac{t}{r}}

$$

应用在此处就为

$$

t=RCln\frac{U_{DD}-U_0}{U_{DD}-U_{th}}\approx RCln2

$$

这边的R就可以当作是管子的导通电阻,而C当作是寄生电容和负载电容的总和通过全响应的公式,其实就可以容易地看出影响传输延迟时间的重要因素,首先是管子的导通电阻由于MOS管的导通电阻一般为几十~几百毫欧,而三极管的导通电阻一般比MOS管大。这样看来好像MOS管的传输延迟时间更小,但不要忘记考虑C的影响。

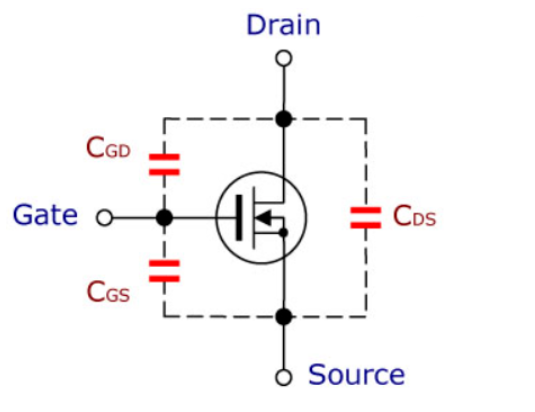

下面就聊聊MOS管的寄生电容,我们可以简单的将其视为具有Cdg、Cgs两个寄生电容,由于MOS管的输入阻抗是可以视为无穷大的,所以输入电流Ig就很小,导致电容充放电过程进行时,时间必然拉得很长。这边就可以等效的看寄生电容C是很大的,这也极大影响了MOS管的传输延迟时间。

其实如果看完上述的讨论后,可能大家会发现传输延迟时间可以理解为受管子的开关速度和电容延迟效应的控制,虽然CMOS具有很好的开关特性,但是其也受电路中寄生与负载电容的影响而致使最后整体的传输延迟时间被拉长。

这边也提醒着我需要提升宏观的思维,刚开始思考这个问题的时候,就是纠结于开关速度对其的影响,没有继续纳入其他因素进行考量。

在surf的时候也发现在考虑温度影响二极管击穿的时候需要注意二极管的击穿方式

Zenerbreakdown

这种发生在高浓度的pn结中,虽然载流子很难碰撞到束缚的价电子,但是随着电压不断升高电场强度增大总有一个场强会使共价键破裂形成电子空穴对。从而击穿当温度升高价电子挣脱束缚的能力越强挣脱后能量更高移动更快自然这样的击穿电压会减小

Avalanchebreakdown

这种发生在低浓度的pn结中,随着反向电压升高,载流子在不断加强的电场中会以足够的动能碰撞束缚的价电子,实现电子空穴对自由移动的电子继续碰撞其他的产生更多的电子空穴对。这种一推二二推四的效应类似雪崩一样,所以名字由此得来。试想温度升高晶格散射加强电子迁移率下降所以平均自由程变短更高的温度下碰撞能量更小因此温度越高击穿电压越高