firpm函数+FPGA_FIR vivado_2022.2具体实操配置

关于仿真以及可能遇到的部分问题可以参考之前两篇博客

【FIR滤波器设计及其FPGA实现】

【FIR IP 核重析】

由于最近开始国赛,所以继续优化FIR滤波器设计以前遗留的问题,此篇博客主要解析

- 更新后没有识别连接的 FPGA 设备

- 更新 vivado 为 2022.2 ,FIR IP 核重构(重点修改)

- FIR 输出直流 or 输出带较大直流偏置

识别FPGA设备 驱动(JTAG-HS2)

如果使用的是JTAG-HS2烧录工具出现vivado无法识别到FPGA设备,可以尝试安装驱动

https://digilent.com/reference/software/adept/start?redirect=1

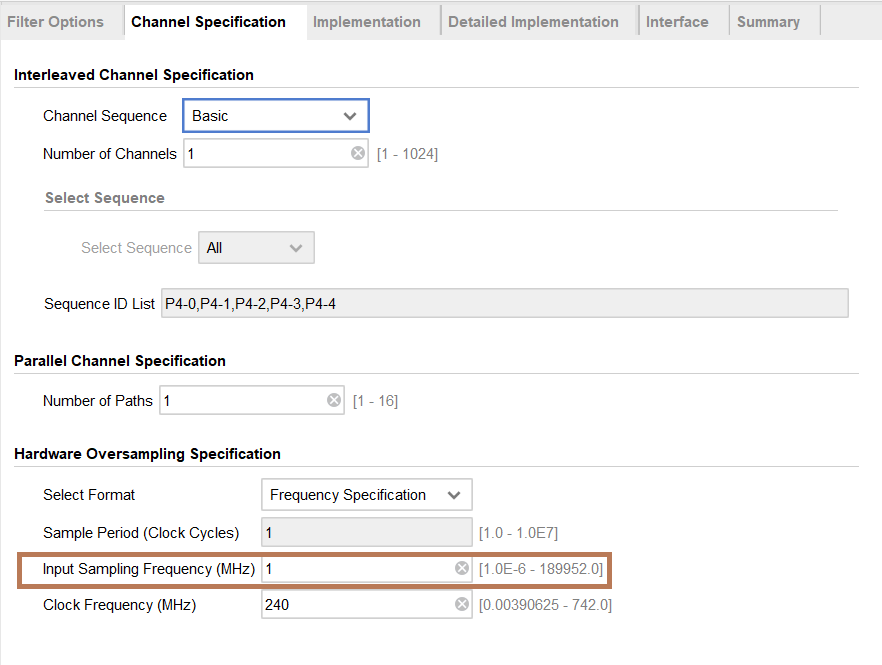

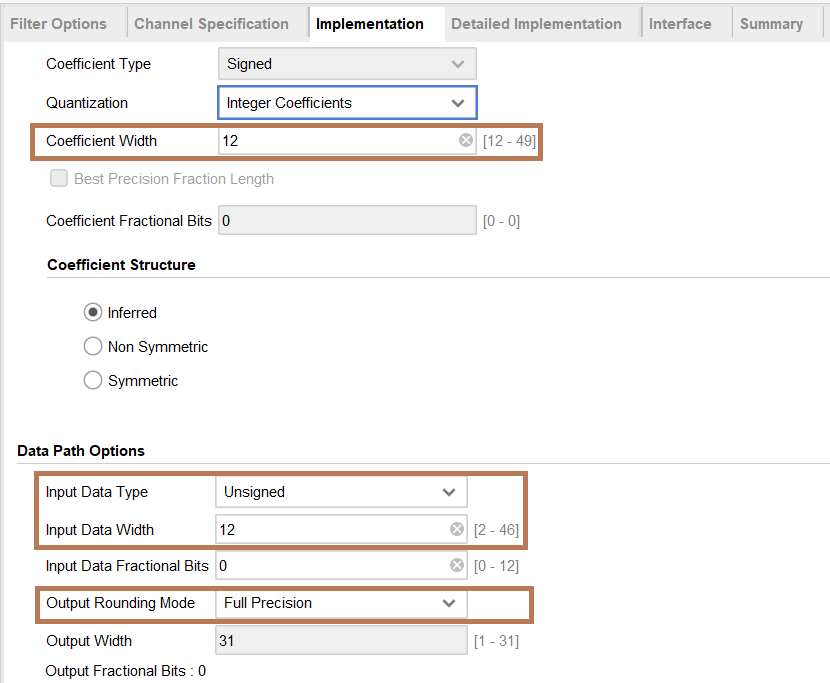

2022.2 VIVADO FIR IP核配置

FIR输出直流问题 or 输出带较大直流偏置解决

输出直流的问题基本可以归结为以下两个原因:

1 | ad9764_dac ad9764_dac_inst ( |

这边注意量化系数加入的位置以及如何计算此系数,这需要参考你使用DA的输出最大电压以及DAC位数。比如我跟hui是使用 14 位的DAC故这边是用 8192 进行比例运算。负偏置需要减去此系数是因为DAC的(0,8192)表示正数,(8192,16384)为负数

如果想要使用 vscode 联动vivado 开发FPGA可以康康🎈🎈

【Vivado × VS Code 配置过程小记】: https://hui-shao.cn/Vivado-%C3%97-VS-Code/?highlight=vs