FIR IP核设置重析 MATLAB~VIVADO联合设计的注意事项

😏之前几篇文章实际上已经基本阐述完了FIR滤波器的基本使用,但是在实际测试的时候难免出现了亿点点问题

- FIR_IP

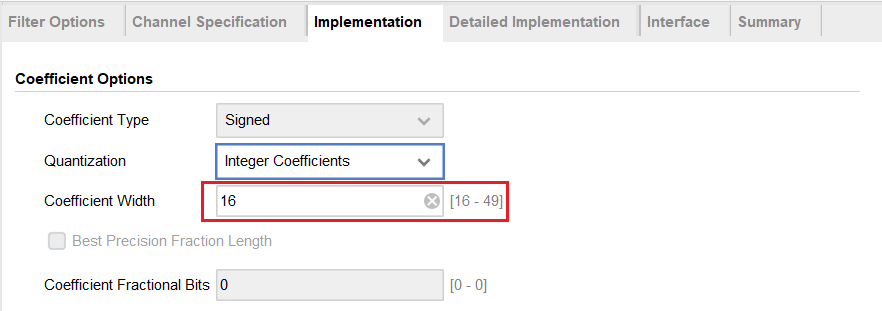

Implementation中的Quantization如何选择Integer Coefficients及Maximize Dynamic Range - 滤波器系数的宽度会影响什么,如何设置12/16

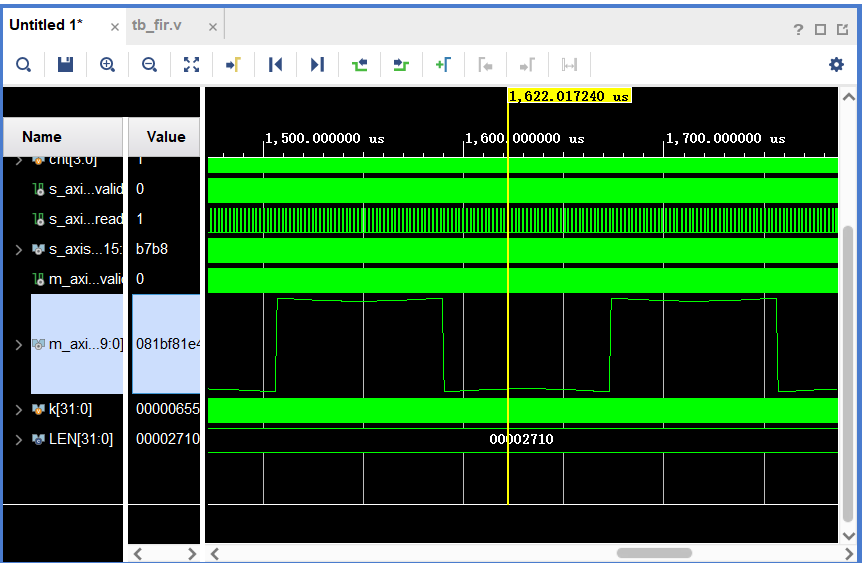

Input Sampling Frequency是什么参数,如何设置其与MATLAB中设计的采样频率以及ADC的采样频率有什么联系,同时降低采样频率后仿真时间不够长会使得看不到输出波形- MATLAB

FDT设计的FIR为什么导入之后报错DSP列不够 - 为什么用之前博客中的仿真代码,改动了输入信号,但是实际VIVADO仿真中没有改完新的输入信号

- 实际测试,输出信号变成圆月弯刀状😇

FIR_IP

Implementation中的Quantization如何选择Integer Coefficients及Maximize Dynamic Range

- 了解IP核里面的选项的含义,最准确实际上应该从VIVADO提供的IP核设计文档中出发,所以如何详细了解看下面

https://docs.xilinx.com/r/en-US/pg149-fir-compiler/Parallel-Data-Channel-Filters

Integer Coefficients整数系数,此选项用于MATLAB已做完滤波器参数量化的情形;不能简单地从字面意义上看认为全动态范围更好,因为其是用在参数没有经过量化的情形,如果你用FDT设计的双精度 or 单精度(非定点),自然可以选择此选项。所以如果直接借鉴之前博客的滤波器设计代码,就直接选择Integer Coefficients就可以。唉,上周跟hui-shao做测试,FIR就一直死,最后发现是这个原因

滤波器系数的宽度会影响什么,如何设置12/16

- 先提一下量化:如果经过量化,虽然精度会掉毕竟上边还取了下整数,但是实际测试效果杠杠的。而且也不会消耗掉很大一部分的存储器与运算资源,毕竟多精度位的运算比较复杂。

- 量化后自然就会引入量化误差,所以这个宽度就是影响量化误差,所以现在我的代码都修改成了16位的滤波器系数

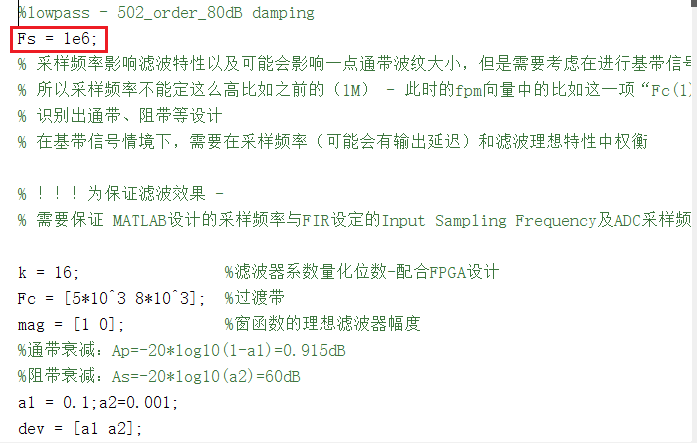

Input Sampling Frequency是什么参数,如何设置其与MATLAB中设计的采样频率以及ADC的采样频率有什么联系,同时降低采样频率后仿真时间不够长会使得看不到输出波形

- 如果按照之前博客的仿真来当然没有问题,不过如果修改了一些参数后比如

Input Sampling Frequency,然后滤波没有实现,别慌,应该就是这个问题 - 开门见山:MATLAB设计的采样频率、IP核中的输入采样频率以及ADC采样频率(输入信号的频率)三者应该一致为效果最好

- 解析:其实提出来结论后就比较容易理解,因为比如我ADC是10M的采样频率,然后MATLAB与IP核中设计的是1M,这就会使得十个点只有一个点进入IP核进行卷积运算,当然就实现不了初定的滤波效果。那肯定就会有提出那直接把MATLAB与IP核的采样频率无脑上拉不就行了,当然是有比较大的问题,因为采样频率的增大,在同等同频带与衰减度设定的条件下,滤波器阶数增长得还是比较快的,一般来说滤波器系数

300~700,可能还会有其他问题,比如非线性失真等等,所以保持三者一致就可以 - 还需要注意的就是输入采样频率也不能太低,不然波形精度、波纹系数比较差,而且输出会有一定的延迟。比如我目前是做一个5k的LPF然后设计的输入采样频率为1M,输出信号就会有一个1ms的延迟,毕竟要采够数据点

MATLAB

FDT设计的FIR为什么导入之后报错DSP列不够

利用MATLAB,FDT设计时,我设定的滤波器系数宽度是16位,但是阶数大概超过726就显示DSP资源不够,但是我自己用

firpm函数以及kasaier窗设计的设计出3000+阶的导入COE文件也没有报错chat推测:这是因为FIR Designer产生的Verilog HDL代码使用了硬件实现的乘法器和累加器来计算滤波器系数。因此,需要的DSP资源与滤波器的阶数成正比。

一种可能的解决方案是减少滤波器的阶数,使其适合可用的DSP资源。您也可以考虑调整滤波器系数宽度,以便更好地满足硬件需求。

另外,自己编写的滤波器设计函数可能采用了不同的算法,并且不会受到MATLAB FIR Designer所限制的DSP资源限制。因此,这可能是为什么使用firpm函数设计的滤波器能够达到更高的阶数而无需报错的原因之一。

这也算是利用firpm的一个优势🥳

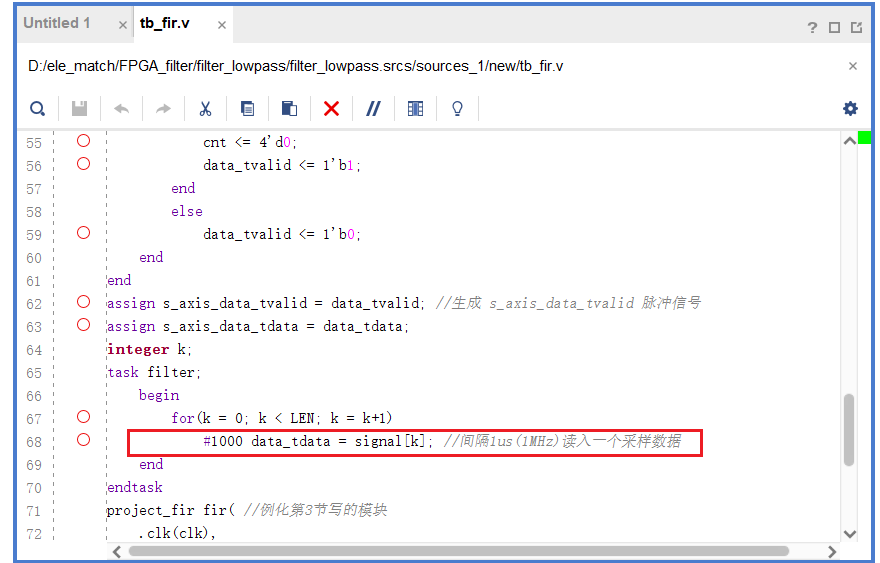

为什么用之前博客中的仿真代码,改动了输入信号,但是实际VIVADO仿真中没有改完新的输入信号

- 这个问题出现我还以为是vivado发病,后面想了想就是少了一部导入

1 | $readmemh("signal_in.txt", signal);//从signal_in.txt中读入采样数据,注意信号文件的存放路径 |

- tb文件读取到的是这个路径下

FPGA_filter\filter_lowpass\filter_lowpass.sim\sim_1\behav\xsim的输入信号文件,所以把新生成的文件添加到此路径下就可以,或者修改下读取的路径

实际测试,输出信号变成圆月弯刀状😇

当时实际测试的时候输出也是这个样子,然后我翻开了之前的博客发现我点了下signed,但是后面意识到ADDA输出的是无符号数,然后就悟了

完善的代码我已经上传git了,同时也对输入采样频率较高时出现点通滤波器现象进行解释

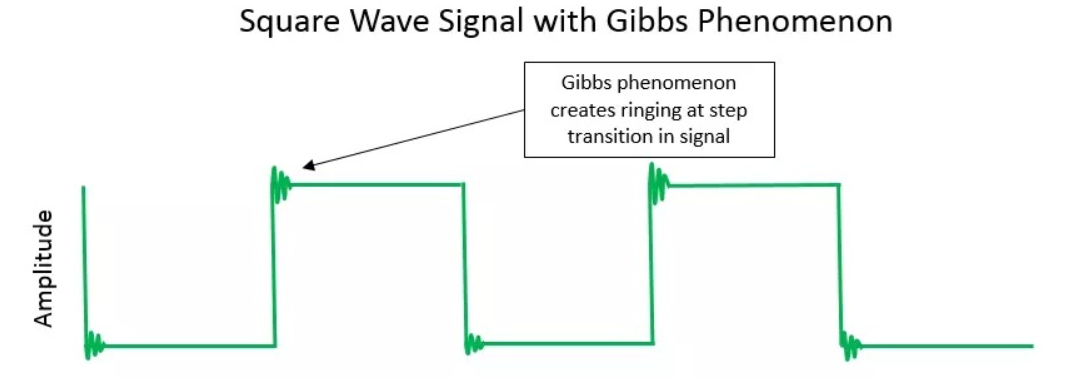

吉布斯现象是指在信号处理中,由于截止频率与带宽限制等因素,信号的频谱出现了明显的振荡现象。在数字信号处理中,可以采用以下方法消除吉布斯现象:

增加采样率:通过增加采样率,可以使信号的频率范围更加充分地表示,从而减少吉布斯现象的发生。

使用窗函数:通过在信号上应用窗函数,可以减少信号在频域上的振荡,从而减少吉布斯现象的发生。

增加滤波器的阶数:通过增加滤波器的阶数,可以使滤波器的频率响应更加陡峭,从而减少吉布斯现象的发生。

使用非线性插值:通过使用非线性插值算法,可以在重构信号时减少吉布斯现象的发生。

使用多项式插值:通过使用多项式插值算法,可以在重构信号时减少吉布斯现象的发生。