2023年电赛H题[信号分离装置]小论

国赛之路,一路逆行,最终还是没能达到自己的既定目标。测评标准不统一也真是6😅。不过这一路走来收获还是繁多,总的来说,尽人事了,只是时候未到。继续努力

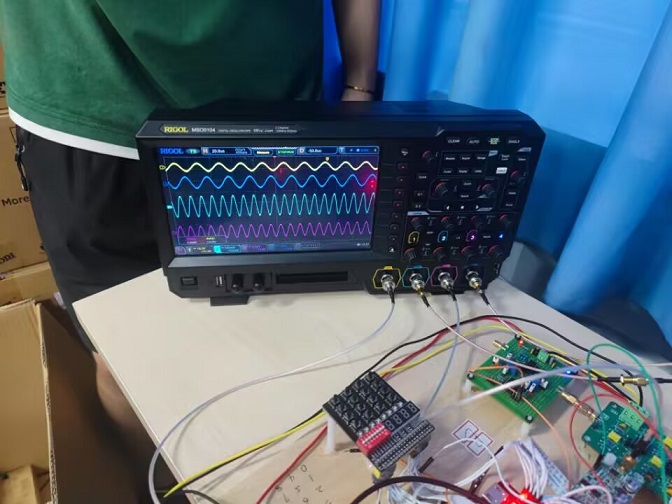

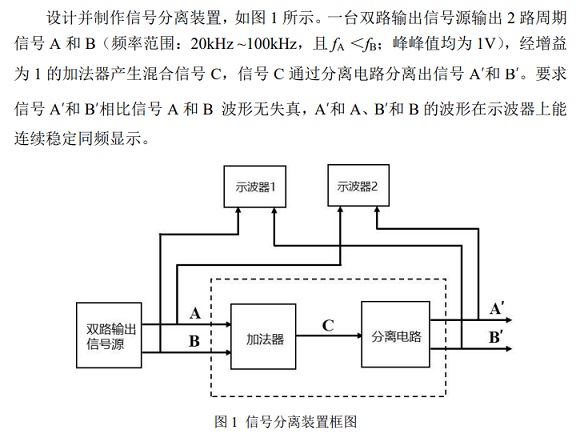

题目解析

经过第一天上午商量核定后,我们这次选择了今年的H题信号分离装置。可惜了今年没有通信系统类题目

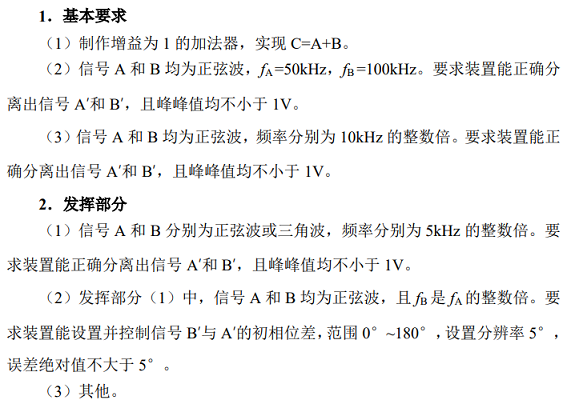

基础要求:加法器 + 定频正弦波分离 + 固定倍数频率的正弦波分离

- 总体来讲基础要求对于大部分(平常没准备的同学)也是比较友好的。信号分离主要可分为硬件和软件方案。硬件:可以用模拟开关 or 拨码开关设置好多阶滤波器。软件:如果用FPGA的话就可以开始拖FIR,因为题目的最高采样频率给到100k,一般来说ADDA LOOP要使得信号无失真恢复,采样频率fs要保证为fh的50倍,不过这时候大概率你会堆if else,这就导致FPGA的DSP资源不够,就需要对选择块进行优化,总的来说还是挺麻烦。而且FIR滤波器需要像我之前博客讲的保证四频大一统。所以这就使得大家都跑去使用重建法

- 重建:重建法实际上就是先用FFT将对应信号A、B的频率进行测定然后加上对应的波形判断(考虑到后续要输出三角波)再利用FPGA ROM表重建原始信号,然后第一天也有同学询问全国组委会是否可以采用这个方案,组委会回复不限制。有趣的就是SD的高水平专家认为这个方案不符合题目的原意,真是独树一帜。这也导致我们做很久的锁相也就是稳频跟别的组什么都没做的最后落到同一个境地,还好当时最后一天比较器、滤波器发病了,然后我去修了相位设置那块。

实际上按照我们原定计划是实现双模分离:FIR滤波器 + 频谱分析重建,这是因为如果纯用FIR滤波的话,如果测评点给的是*(20k三角波、60k的正弦波)*阁下应该如何应对。不过这是后话了,因为我们调FPGA的FFT仿真出来跑得很欢,但是最后实际使用的时候就是不行,我队友hui-shao又把它干成串行存储RAM然后读取比较分析,还是危,所以我们后续是先用32测好频谱和识别波形再通过通俗的电平通信告诉FPGA,也就是FPGA此时就相当于起到DDS的作用。

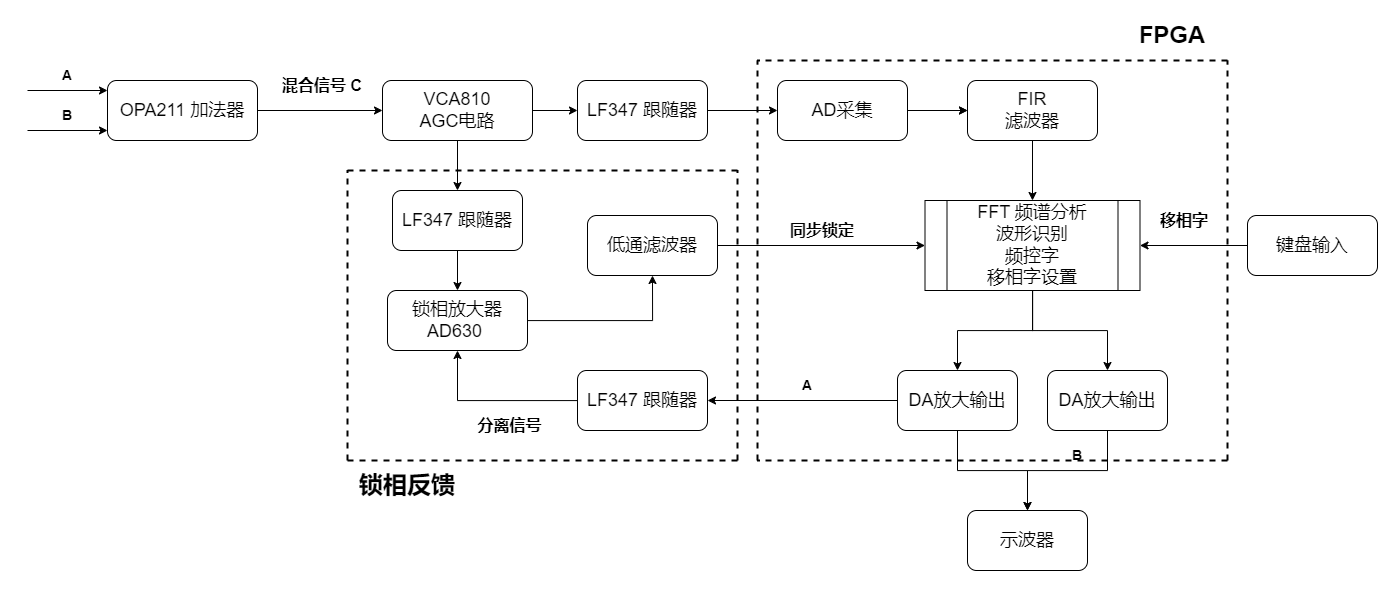

设计框架解析

前级硬件调理电路主要特别就是用到VCA810的AGC电路这主要是我们考虑到如果输入两路信号在有初始相位差的情况加法器输出信号幅度不定,但是很明显最终测评点并没有在这点卡,有点不理解测评点不应该反映一个系统是否完善吗(不做评价)。然后我们加了两级之前准备的跟随器,这是因为混合信号C在这边要一分二,一路进入后级的重建模块,一路进入锁相反馈模块。

锁相反馈:

实际上这道题原来应该是考察反馈的引入,通过这个引入的反馈使得最终重建的信号无限逼近原始信号。

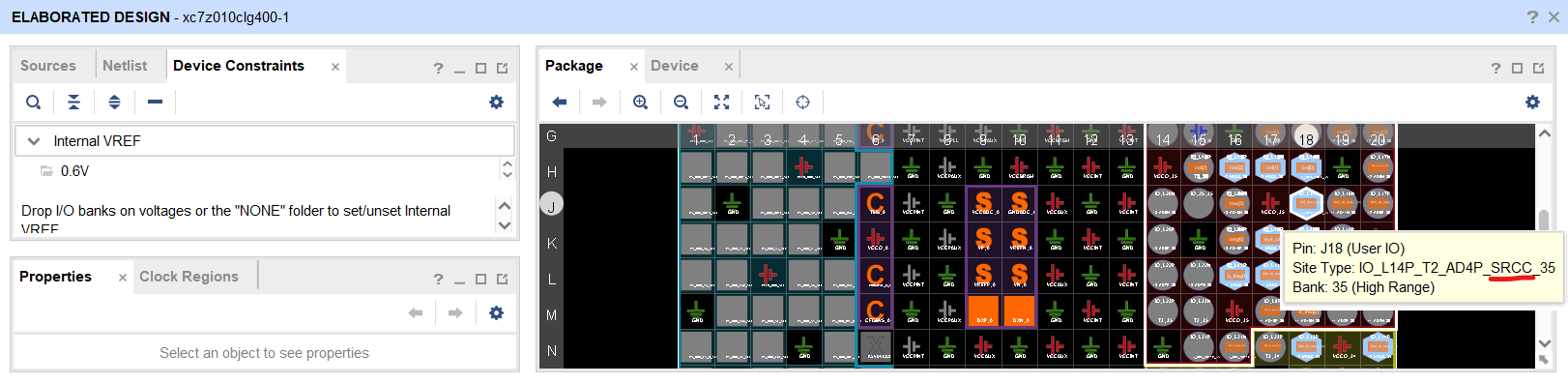

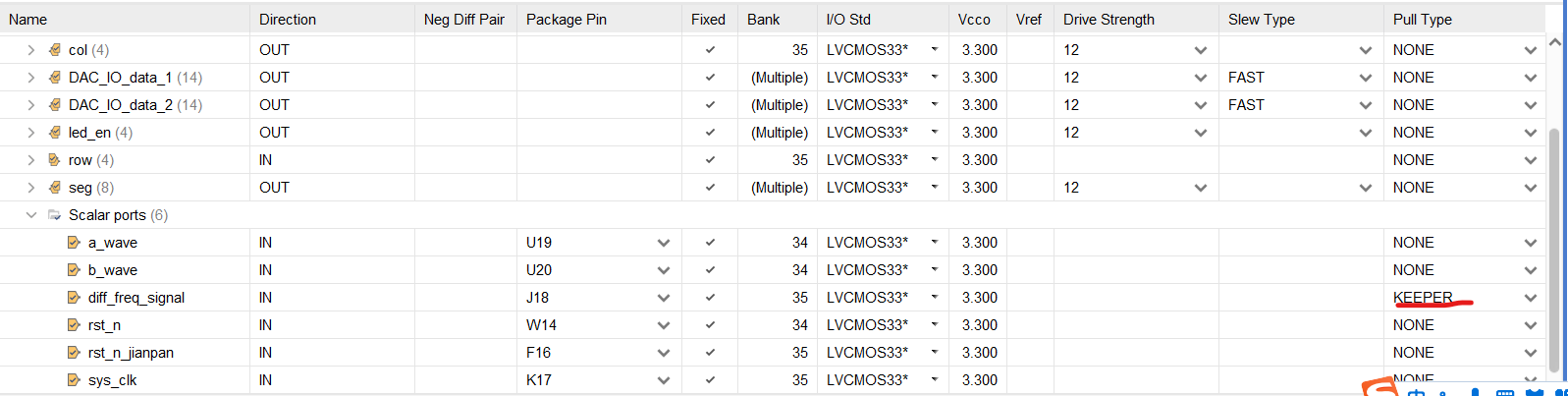

- 硬件方案:1. 将混合信号C和通过DAC输出的重建信号输入到AD630的参考信号端和待测信号端,就可以得到两者的频差信号,此时的AD630锁相放大器起到乘法调理的作用,因为积化和差的关系就会出来很多信号所以需要通过一个有源LPF(设置截止频率为1k)来得到频差信号,再通过 FPGA 设计等精度测量方式引出SRCC的IO口并且设置位keeper模式,且保证整体系统的时钟大一统,就可以准确测得频差信号的频率然后再通过频控字补偿回去。

- 有心的人很快就会发现一般来说频差信号的频率总是很小的,因为在频控字位宽上调后,实际上频率分辨率是非常高的。但是频率一旦小,测量时间就需要变长,所以我们采用的是刚开始频谱分析完并不是输出一个十分准确的频率比如如果分析结果为50k,我们设计的DAC输出频率为49.5k,此时就可以使得频差信号的频率变大,测量时间也就拉上去了,实际上比较好的算法应该是测量多次频差然后最终补偿到原始信号频率。

当然也有很多人投机取巧(大部分吧,就是简单拟合,不做闭环)这就很赌博,如果信号发生器的晶振并不是准确的标识频率,这就危了,实测下来应该是要稳定到0.001Hz的分辨率基本就没有频漂

这应该是比较好的硬件反馈方案了,当然我们当时还想到一个应该来说更佳的方案,将原始信号直接倍频作为DAC输出的时钟,软件那边魔改PLL IP核已经实现了16倍频,但是硬件锁相环死了🤔

软件方案:软件锁相实际上方案还是比较多的,PID、数字锁相环、带通采样运用。PID由于我不是控制的所以只懂皮毛吧,数字锁相环应该可以看看Xilinx的IP核应该可以做同步,这次就类似于实现帧同步。当然还有一个比较惊艳的同步锁定方案就是带通采样的运用。做反馈环路无非就是想得到重建信号与原信号的频差信号,于是我们规定采样频率为5k,假设输出重建信号的频率为25.1k那么此时用5k采样频率的ADC采样得到的信号频率为100Hz,这是因为如果把25.1k当作带通信号的话,则根据带通采样原理其会被搬移到 [0 5k]的频谱范围内而题目不是正好输出信号都是5k的整数倍吗😌,这时候再把这个频率补给频控字。

设置初相位差:这个按照正常人的理解都应该是装置能够设置并控制分离信号A‘、B’的初相位差,但是SD省认为是要原始信号多少初相位差这边就是输出多少,真的6啊。

- 具体做法就是准备一个键盘然后在FPGA中写好键盘识别与锁相模式进入,因为首先要知道A路、B路分离信号如果没有加入频控字修正应该是同步输出的,但是由于我们加入了一定的频控字修正字,两者就不是同步的了,所以我的做法是当我键盘上输入四位数(三位相位字,一位任意锁定字)这时候会有一个valid信号然后利用这个valid信号来决定是否加上频控字,一旦valid有效,那么接入到后面输出DDS模块的频控字为初始设定,此时两者就是被锁相同步然后再按一下启动键就会设置到键盘规定的相位。下面公式C就是加入的频控修正字,这就会导致两者不同步输出。

$$

A/B ≠(A+C)/(B+C)

$$

- 具体做法就是准备一个键盘然后在FPGA中写好键盘识别与锁相模式进入,因为首先要知道A路、B路分离信号如果没有加入频控字修正应该是同步输出的,但是由于我们加入了一定的频控字修正字,两者就不是同步的了,所以我的做法是当我键盘上输入四位数(三位相位字,一位任意锁定字)这时候会有一个valid信号然后利用这个valid信号来决定是否加上频控字,一旦valid有效,那么接入到后面输出DDS模块的频控字为初始设定,此时两者就是被锁相同步然后再按一下启动键就会设置到键盘规定的相位。下面公式C就是加入的频控修正字,这就会导致两者不同步输出。

我热爱竞赛,会为每一次调出功能非常激动,即使最后结果并不如愿,但是以后翻看这段电赛时光应该还是非常怀念的。看看自己的作品还是很开心。感谢我的队友🧐

最后希望大家如果用FPGA打的话如果还没入坑,可以试试Altera,vivado编译,综合真的慢。还有就是ZYNQ尽量叉出去,因为到最后你写好还得用VITIS固化再烧到FLASH,难免发病,还有就是7010 DSP太少啦,建议冲ARTIX 200T