FIR滤波器 窗函数详解、MATLAB Filter Designer解读

之前虽然对FIR滤波器的vivado实现、串行并行结构已经详述,但是对于为什么要加窗函数、以及MATLAB使用Filter Designer工具进行设计没有进行研究,本篇也是做此工作

加窗的意义、窗函数的选择

- 在上一篇提到FIR、IIR有一个区别就是前者是有限冲激响应、后者是无限冲激响应,但是滤波器的系数在时域上是无限响应的,为了实现FIR的有限我们就需要加窗截断,故可以说这边加窗的意义就是 - 截断

- 具体的数学公式推导可以看看下面这篇

https://zhuanlan.zhihu.com/p/40394935

这就首先得讲一下,滤波器设计关心的一些参数

- 过渡带宽

- 通带边沿衰减

- 阻带最小衰减

- 通带波纹…

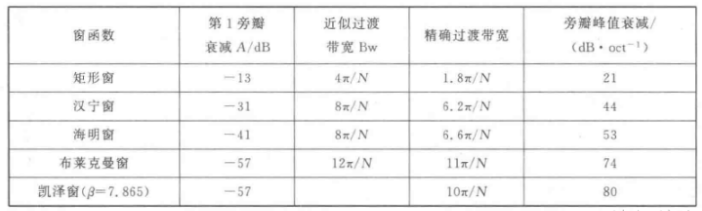

关于窗函数的选择实际上是基于系统需要怎么样的滤波器性能,例如我们需要阻带衰减为50dB,而矩形窗和汉宁窗最高也就做到21、44dB,无论阶数设置得再高也没办法做到50dB,就类似于这个选择标准;而可以从表格中看出,如果给定带宽指标,实际上是可以直接计算出相应的近似N(阶数)的

- 实际上选择也是中庸之道 - 综合考虑旁瓣幅度、阻带衰减、主瓣宽度等

- 解释:当选用主瓣宽度较窄时,虽然得到的幅频特性较陡峭,但通带、阻带波动会明显增加;当选用较低的旁瓣幅度时,虽然得到的幅频特性较平缓匀滑,但过渡带变宽

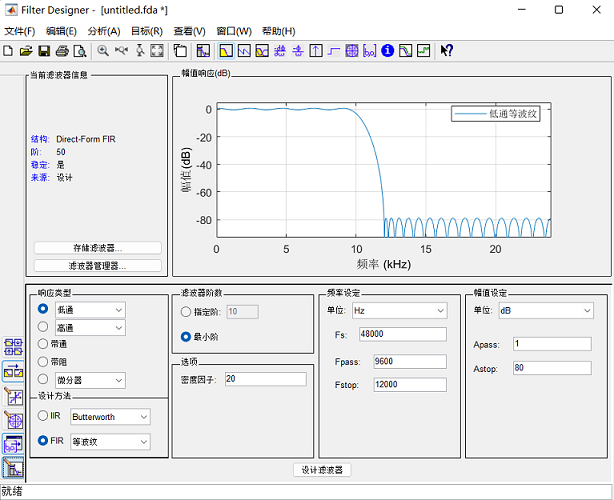

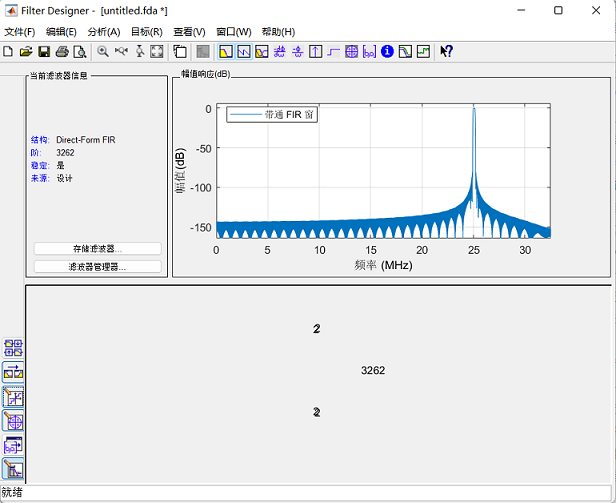

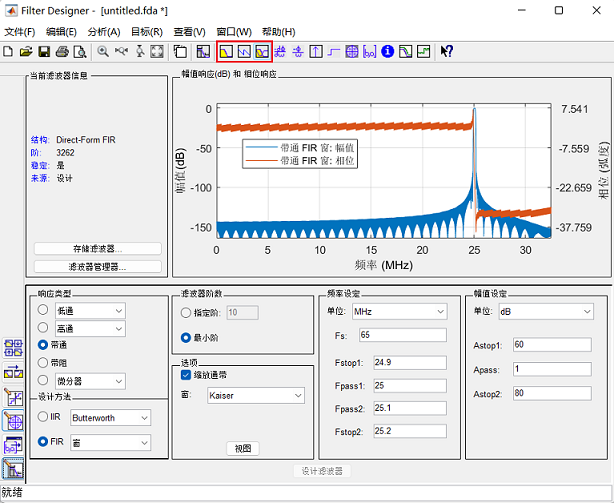

Filter Designer

这边主要对FIR滤波器的一些设定进行解释

实际上实现FIR滤波器的方式有很多种,但是总得搞清楚为什么要选择窗函数吧😏😏所以我问了下

- 实际上窗函数的设计法已经涵盖基本所有我们需要的参数设定场景,你甚至可以自己写窗来实现

- 实际应用中,可以根据权重较高的参数进行窗函数选择,但是也需要考虑阶数不能过大(例如我下面设置的25M中心频率、带宽为0.3M的60dB BPF)就3000+!的N。但是实际上经过实际测试后发现其并不对vivado资源占用太大,甚至很小。也可能因为我们上的是ZYNQ7010的板子

高阶数会出现的问题以及大概范围

- 计算复杂度增加:随着滤波器阶数的增加,计算复杂度也会相应地增加,这意味着需要更多的资源来执行滤波操作。过高的阶数可能会使系统性能受到限制

- 采样频率降低:高阶FIR滤波器需要更多的时间来处理信号,这可能导致采样率下降。在某些应用程序中,这可能会影响信号质量

- 存储器需求增加: 需要存储输入数据和滤波系数的存储器的需求随着滤波器阶数的增加而增加,这可能会导致设计所需的存储器资源变大

- 滤波特性不稳定:高阶FIR滤波器可能会引入不稳定的滤波特性,这可能会导致频率响应的异常行为或者振荡

- 实际设计时,需要评估阶数和计算与存储资源消耗的平衡,并根据应用场景需求来确定FIR滤波器的阶数,一般300 ~ 500阶以下为正常范围,高要求系统中1000以上跑问题也不大

这边设计完成后也可以康康具体的幅频、相频响应

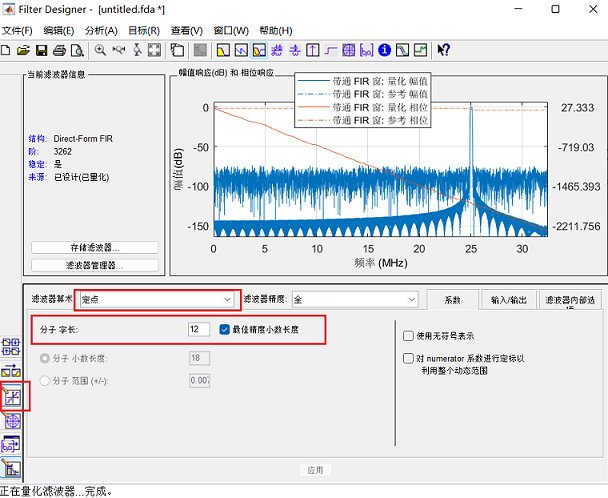

- 设置一下与IP核对应的滤波系数位宽

- 需要载一个

Fixed-point...的拓展包

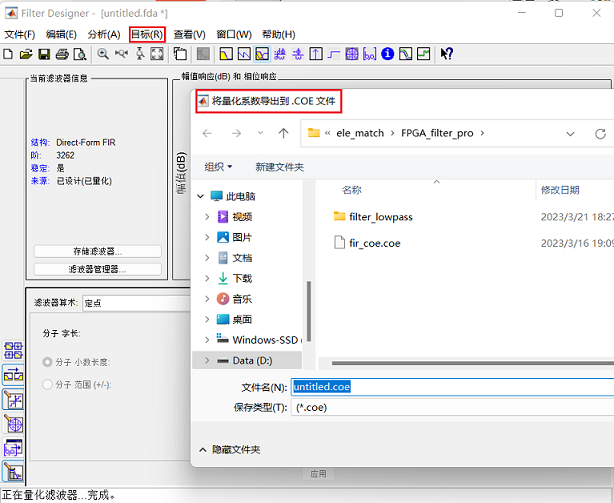

- 导出COE文件就行

余下的vivado配置步骤就与之前一样

纪念

今天FPGA Wireless download有点大进展😁😁