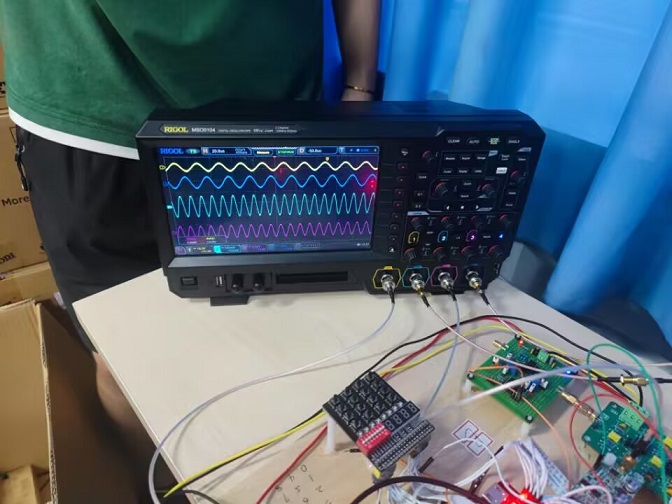

2023年电赛H题[信号分离装置]小论

国赛之路,一路逆行,最终还是没能达到自己的既定目标。测评标准不统一也真是6😅。不过这一路走来收获还是繁多,总的来说,尽人事了,只是时候未到。继续努力

今天进行ASK信号解调开发的时候,ADDA、判决门限等需要有一个较低的时钟来驱动。但是vivado自带的PLL和MMCM出的频率最低是6.25MHz左右,所以比如我这边需要一个100kHz的时钟,这就需要自己利用sys_clk自定义分频生成一个衍生时钟。

关于仿真以及可能遇到的部分问题可以参考之前两篇博客

【FIR滤波器设计及其FPGA实现】

【FIR IP 核重析】

由于最近开始国赛,所以继续优化FIR滤波器设计以前遗留的问题,此篇博客主要解析

很久没更博啦,前段时间一直忙着备考,这几天终于可以摸鱼会😎之前一直想写一篇阅读datasheet的博客,但是拖到现在(这学期有点麻)。因为电赛我们队也有准备通信方向,然后模拟混频器也是需要准备的模块,所以这次就以AD835乘法器来作为讲解案例

LCD调试可以正常使用,但是烧录后不正常工作。

😏之前几篇文章实际上已经基本阐述完了FIR滤波器的基本使用,但是在实际测试的时候难免出现了亿点点问题

Implementation中的Quantization如何选择Integer Coefficients及Maximize Dynamic RangeInput Sampling Frequency是什么参数,如何设置其与MATLAB中设计的采样频率以及ADC的采样频率有什么联系,同时降低采样频率后仿真时间不够长会使得看不到输出波形FDT设计的FIR为什么导入之后报错DSP列不够串联谐振回路属实是不容易过的坑,一直在挖坑的路上,不过坚持着仿真和思考也还是有一定的收获,首先坑就是如下:为什么会出现平坦区,而出现平坦区前为什么在低频段又会有下降呢,这个下降的速率有受什么的影响……

之前虽然对FIR滤波器的vivado实现、串行并行结构已经详述,但是对于为什么要加窗函数、以及MATLAB使用Filter Designer工具进行设计没有进行研究,本篇也是做此工作

通信题的纯数字方案中FM调制的FPGA实现显得尤为重要,之前一段时间一直在跟着我查大哥整理收发机的一些原理,然后就是时不时问辉说怎么实现FM调制(初期嘛,一直搞不清楚AM、FM哈哈😏😏),现有终于对收发机的原理以及常见结构有点小悟,下面主要就是对FM调制的实现做一个工程开发记录,具体理论这边就不赘述

在上一次博客Fir滤波器设计及其FPGA实现里具体阐述了如何设计FIR滤波器并在vivado上面进行仿真,这边主要是补充FIR的原理和串并行结构的差异与如何配置,以及FIR ~ IIR的差别